¿Qué es PCIe?

PCIe (Peripheral Component Interconnect Express) es un estándar de bus de expansión de alta velocidad diseñado para reemplazar los estándares de bus PCI, PCI-X y AGP

Es la interfaz común de la placa base para las tarjetas gráficas, tarjetas de sonido, adaptadores de host de unidades de disco duro, SSD, conexiones de hardware Wi-Fi y Ethernet en las computadoras personales

PCI vs PCIe

PCI y PCIe son dos estándares de bus de expansión que se utilizan para conectar dispositivos de hardware a la placa base de una computadora. A continuación, se describen algunas diferencias importantes entre PCI y PCIe:

- Interfaz: PCI es una interfaz paralela, mientras que PCIe es una interfaz serial

Esto significa que PCIe puede enviar y recibir datos en dos direcciones al mismo tiempo, lo que lo hace mucho más rápido que PCI

- Velocidad: PCIe es mucho más rápido que PCI

La velocidad de transferencia de datos de PCIe es de hasta 32 Gbps para PCIe 3.0, mientras que la velocidad de transferencia de datos de PCI es de hasta 133 MB/s

- Ranuras: Las ranuras PCIe son más pequeñas que las ranuras PCI

Además, las ranuras PCIe pueden tener diferentes tamaños físicos, dependiendo del número de carriles conectados a la ranura

- Compatibilidad: PCIe es compatible con versiones anteriores de PCI, lo que significa que una tarjeta PCIe de una versión anterior se puede utilizar en una ranura PCIe de una versión más reciente, aunque la velocidad de transferencia de datos se limitará a la velocidad de la ranura

|

|

PCI |

PCIe (PCI Express) |

|

Nombre de formato largo |

Interconexión de componentes periféricos |

Interconexión Express de componentes periféricos |

|

¿Qué es? |

Un estándar de bus de computadora local |

Un estándar de bus de expansión de computadora en serie de alta velocidad |

|

Uso primario |

Provisión de una interfaz estandarizada para conectar hardware periférico a la placa base de una PC |

Una interfaz de alta velocidad para conectar hardware periférico a la placa base de una PC |

|

Versión inicial |

1990 |

2004 |

|

Desarrolladores influyentes |

Laboratorios de arquitectura, Intel Corporation |

Grupo de trabajo Arapaho (AWG), Intel, PCI SIG |

|

Número de versiones |

6 (más reciente: 3.0) |

7 (más reciente: 7.0) |

Algunas características importantes de PCIe son:

Líneas: El enlace PCIe se construye alrededor de parejas unidireccionales dedicadas de conexiones serie (de 1 bit), punto a punto, conocidas como líneas

Ranuras: Cada placa base de PC de escritorio tiene un número de ranuras PCIe que se pueden usar para agregar tarjetas gráficas, tarjetas RAID, tarjetas Wi-Fi o tarjetas de expansión SSD

Versiones: Hay varias versiones de PCIe en uso hoy en día, incluyendo PCIe 1.0, PCIe 2.0, PCIe 3.0 y PCIe 4.0

Cada versión tiene una velocidad de transferencia de datos diferente y un número diferente de líneas.

Las ranuras PCIe están diseñadas para ser compatibles con versiones anteriores, lo que significa que una tarjeta PCIe 4.0 se puede usar en una ranura PCIe 3.0, pero la velocidad de transferencia de datos se limitará a la velocidad de la ranura

El número de líneas PCIe disponibles en una placa base varía según el modelo y el fabricante. Las placas base suelen tener varias ranuras PCIe, cada una con un número diferente de líneas. Los puertos PCIe más comunes son PCIe x1, PCIe x4, PCIe x8 y PCIe x16

- El puerto PCIe x16 es el más común en las placas base y se caracteriza por ofrecer 16 líneas PCIe

- Las placas base de gama media y alta suelen tener dos o más puertos PCIe x16

- Es importante destacar que aunque un producto físicamente tenga una conexión PCIe x16, puede ser que no ocupe todas las líneas. Es relativamente común encontrar productos con conector x16, pero que habilitan solo 8 líneas PCIe o menos

- En resumen, el número de líneas PCIe disponibles en una placa base depende del modelo y del fabricante, pero el puerto PCIe x16 es el más común y ofrece 16 líneas PCIe.

| Versión | x1 | x2 | x4 | x8 | x16 |

|---|---|---|---|---|---|

| PCIe 1.0 (2.5 GT/s) | 500 MB/s | 1 GB/s | 2 GB/s | 4 GB/s | 8 GB/s |

| PCIe 2.0 (5 GT/s) | 1 GB/s | 2 GB/s | 4 GB/s | 8 GB/s | 16 GB/s |

| PCIe 3.0 (8 GT/s) | 2 GB/s | 4 GB/s | 8 GB/s | 16 GB/s | 32 GB/s |

| PCIe 4.0 (16 GT/s) | 4 GB/s | 8 GB/s | 16 GB/s | 32 GB/s | 64 GB/s |

| PCIe 5.0 (32 GT/s) | 8 GB/s | 16 GB/s | 32 GB/s | 64 GB/s | 128 GB/s |

| PCIe 6.0 (64 GT/s) | 16 GB/s | 32 GB/s | 64 GB/s | 128 GB/s | 256 GB/s |

| PCIe 7.0 (128 GT/s) | 32 GB/s | 64 GB/s | 128 GB/s | 256 GB/s | 512 GB/s |

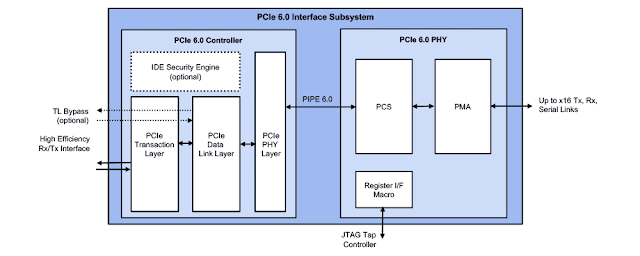

PCI 6.0

Lo primero que nos interesa del

PCI Express 6.0 es saber cuanta información podemos transmitir por segundo a

través de esta interfaz. No olvidemos que en las placas base de nuestros PC

podemos encontrar interfaces de 1, 4, 8 y hasta 16 líneas diferentes, donde en

cada una se envían datos en paralelo. ¿El ancho de banda total? 256 GB/s en

ambas direcciones para la interfaz utilizada en tarjetas gráficas y 64 GB/s

para la de los SSD M.2. Eso sí, hemos de tener en cuenta que estamos hablando

del ancho de banda sumado en ambas direcciones, es decir, teniendo en cuenta

lectura y escritura al mismo tiempo.

Compatibilidad hacia atrás

La interfaz PCI Express ha sido

siempre compatible hacia atrás con versiones anteriores del protocolo, esto

significa que podemos conectar una tarjeta PCI Express 1.0 en un slot PCI

Express 6.0 y funcionará debido a que el pinaje va a ser exactamente el mismo.

Esto es un arma de doble filo, ya que para aumentar el ancho de banda no se

pueden colocar pines adicionales y, por tanto, se ha de aumentar la velocidad

de reloj a la que funciona la interfaz. Es decir, los bombeos de datos por

segundo para transmitir los datos.

¿El problema con el PCI Express

6.0? A medida que aumentamos la velocidad de reloj de una interfaz esta se va

volviendo más inestable con la distancia y después de seis generaciones han

tenido que hacer cambios en la interfaz debido a la alta velocidad a la que

funciona la interfaz de manera tradicional. El problema viene cuando para

transmitir 256 GB/s en una interfaz Full Duplex. La cual permite transmitir 1

bit por cada dirección simultáneamente, necesitamos que la velocidad de la

interfaz suba hasta 128 GHz y a esas velocidades la integridad de la señal se ve

seriamente comprometida.

Esto ha obligado a adoptar una

serie de medidas para hacer posible el salto al PCI Express 6.0, empezando por

la codificación.

PCI Express 6.0 y codificación

PAM4

¿Cómo sabe una interfaz externa o

interna de un chip si el valor es un 1 o un 0? Pues sencillo, dependiendo del

voltaje en el que se transmite la información. Los sistemas binarios se basan

en el uso de dos voltajes con la suficiente distancia entre ellos para que la

bajada o subida de voltaje haga que la señal no se confunda. En los sistemas

analógicos una simple variación en el voltaje supone un cambio en la

información. Por ese motivo los ordenadores hablan en binario.

¿Qué tiene que ver esto con el

PCI Express 6.0? Dado que no podemos aumentar el ancho de banda porque la señal

se distorsiona y tampoco el número de pines por compatibilidad hacia atrás se

ha de buscar una solución y esta pasa por el uso codificación PAM4 o Pulse

Amplitude Modulation, la cual ya hemos visto en la GDDR6X y no se basa en el

uso de dos valores de voltaje sino de 4 valores de voltaje por cada pin. De

esta manera podemos codificar los valores 00, 01, 10 y 11 en cada pin. Cuatro

valores en total, en vez de los dos valores clásicos que serían 0 o 1.

La solución evita aumentar el

ancho de banda y los pines, pero nos adelanta que en el PCI Express 7.0 ya no

será posible desde los métodos convencionales. Quizás veamos el uso de fotónica

y de interfaces ópticas, pero con las mejoras del PCI Express 6.0 recién

salidas del horno, mejor tener paciencia con su sucesor.

Cambios en el sistema de

paquetes

El salto a PAM-4 ha cambiado la

forma en la que la interfaz PCI Express 6.0 envía sus paquetes, pese a que es

compatible con las generaciones anteriores a base de comunicarse en el tradicional

modo PAM-2 o NRZ. La realidad es que el formato PAM-4 no soporta el sistema de

paquetes anterior y, por tanto, el protocolo de comunicación ha cambiado debido

a ello.

Forward Error Correction

El primer cambio ha sido el

llamado Forward Error Correction o FEC, el cual es el nuevo protocolo para

corregir los errores en el envío de los datos. El problema es que el ancho de

banda a procesar es tan alto que el FEC añade una enorme latencia al envío de

los datos. Para paliar esto en el estándar PCI Express 6.0 se utiliza un tipo

de paquete llamado FLIT. Un paquete no es más que un conjunto de bits con un

destino en concreto. ¿La latencia de envío de cada FLIT? Depende de la cantidad

de líneas de la interfaz, pero cada paquete tiene una latencia de solo 2 ns en

un PCI Express 6.0 de 16 líneas, pero llega hasta los 32 ns en una interfaz con

una sola línea.

El FEC solamente trabaja con

tamaños fijos, es por ello que el FLIT tiene un tamaño de 256 bytes por envío.

Cada paquete o TLP puede tener un tamaño que va de los 0 bytes a los 4096 bytes

y, por tanto, cada paquete puede estar compuesto por varios FLITS.

Cyclic Redundancy Check

La comprobación redundante

cíclica es un sistema de corrección de errores en el código que se usa

normalmente en unidades de almacenamiento y en redes digitales y que se ha

integrado dentro del estándar PCI Express 6.0 para comprobar que los datos

transmitidos de extremo a extremo mantienen su integridad y ni un solo bit se

ha visto cambiado en el proceso.

Esto se consigue con una serie de

cálculos polinomiales realizados por una serie de unidades especializadas para

ello que se van a incluir con la interfaz. Esto es algo que tiene sentido con

la enorme cantidad de datos que se van a transmitir y supone un ahorro en el

caso de los futuros fabricantes de los M.2 SSD que no van a tener que añadir

esta funcionalidad en sus unidades de estado sólido al ya venir de serie el CRC

en la interfaz.

Nuevo modo de bajo consumo en PCI Express 6.0

El PCI Express 6.0 añade un nuevo

estado de bajo consumo bautizado como L0P. Este modo le permite a la interfaz

recortar su consumo energético cuando el flujo de datos que se envía es más

bajo de los que puede transmitir la interfaz. Para ello varía la velocidad de

reloj a la que esta funcione para los momentos puntuales en los que los datos a

transmitir se encuentran en menor volumen.

Este mecanismo se encuentra

estrechamente relacionado con las nuevas tecnologías introducidas en la sexta

versión del PCIe 6, por lo que solo se podrá utilizar con dispositivos

compatibles con esta generación de la interfaz.

Se puede usar una PCIe x1en un slot PCIe x16

¿PCie funciona en portátiles?

¿Es posible añadir una ranura PCIe a un portátil?

¿Cómo se puede añadir una ranura PCIe a un portátil?

Cómo aumentar la velocidad de las tarjetas PCI (En 4 Pasos)

Enciende la computadora y presiona el tecla "Suprimir" antes que aparezca el logo de Windows para abrir el BIOS (Basic Input/Output System - Sistema básico de entrada y salida).

Presiona las teclas "Ctrl" y "F1" al mismo tiempo para revelar las funciones avanzadas del BIOS.

Utiliza las flechas direccionales para seleccionar la opción "PnP/PCI Configuration" (Configuración PnP/PCI). Después, selecciona la opción "PCI Latency Timer" (Temporizador de latencia PCI) y presiona "Entrar". Dependiendo de cuánto quieras aumentar la velocidad de la tarjeta PCI, selecciona entre "64" ó "128" y presiona "Entrar".

Presiona "Esc" para volver al menú principal del BIOS. Selecciona "Save Settings and Exit" (Guardar configuración y salir) y presiona "Entrar" para completar el proceso de aceleración de la tarjeta PCI.